Reconfigurable Computing Research Laboratory

# DIGITAL LOGIC DESIGN VHDL Coding for FPGAs Unit 2

- ✓ CONCURRENT DESCRIPTION

- 'with-select', 'when-else' statements

- Arithmetic expressions, integer type, type conversions.

- Examples: multiplexor, LUT, decoder, tristate buffer

# ✓ CONCURRENT DESCRIPTION

- In this description, the order of the statements is irrelevant: all the statements represent circuits that are working at the same time. This type of description is wellsuited for combinatorial circuits.

- The use of sentences with 'and', 'or', 'xor', 'nand', 'nor', 'xnor', and 'not' is a basic instance of the concurrent description. It is sometimes called 'horizontal description'.

- In Unit 4, the so-called 'structural description' is just a generalization of the concurrent description.

- Since we already know how to build circuits based on logic gates, we now present two concurrent assignment statements (*with - select, when - else*), which are far more powerful than the statements with logic gates when it comes to describe complex circuits.

- CONCURRENT ASSIGNMENT STATEMENTS:

- Selected Signal Assignment: WITH-SELECT: This statement allows assigning values to a signal based on certain criterion.

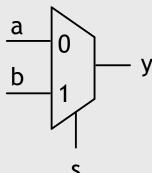

- MUX 2-to-1:

$a = \begin{bmatrix} s & a & b & y & s & y \\ 0 & 0 & 0 & 0 & 0 & 0 \\ 0 & 0 & 1 & 0 & 1 & b \\ y & 0 & 1 & 0 & 1 & b \\ 0 & 1 & 1 & 1 & 1 & 1 \\ 1 & 0 & 0 & 0 & 0 \\ 1 & 0 & 1 & 1 & 1 & 1 \\ 1 & 1 & 0 & 0 & 0 \\ 1 & 1 & 1 & 1 & 1 & 1 \end{bmatrix}$  $y = \overline{s}(a \ \overline{b} + a \ b) + s(\overline{a} \ b + a \ b)$  $y = \overline{sa} + sb$

with s select: 's'specifies the selection criterion when specifies the value assigned to 'y' for each value of 's' when others: we need to include all the possible values of 's', that are 9 according to *std\_logic* type.

library ieee; use ieee.std\_logic\_1164.all;

#### Selected Signal Assignment (WITH – SELECT):

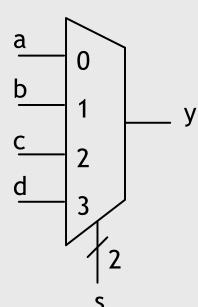

#### • MUX 8-to-1

Reconfigurable Computing Research Laboratory

```

library ieee;

use ieee.std_logic_1164.all;

```

```

entity my mux81 is

а

port ( a,b,c,d,e,f,g,h: in std logic;

0

b

s: in std logic vector (2 downto 0);

1

y: out std logic);

С

2

end my mux81;

d

3

У

architecture struct of my mux81 is

е

4

begin

f____

with s select

5

y <= a when "000", -- note ',' instead of ';'</pre>

g

6

b when "001",

h

c when "010",

d when "011",

3

e when "100",

S

f when "101",

g when "110",

h when others;

end struct;

```

Selected Signal Assignment (WITH – SELECT):

#### MUX 6-to-1

```

Reconfigurable Computing Research Laboratory

```

```

library ieee;

use ieee.std_logic_1164.all;

а

0

entity my mux61 is

b

port ( a,b,c,d,e,f: in std logic;

s: in std logic vector (2 downto 0);

С

2

У

y: out std logic);

d

3

end my mux61;

4

architecture struct of my mux61 is

5

begin

with s select

S

y <= a when "000",

b when "001",

c when "010",

d when "011",

e when "100",

Value '-': Don't care output

f when "101",

It helps the synthesizer to <

('-') when others;

optimize the circuit

end struct;

Daniel Llamocca

```

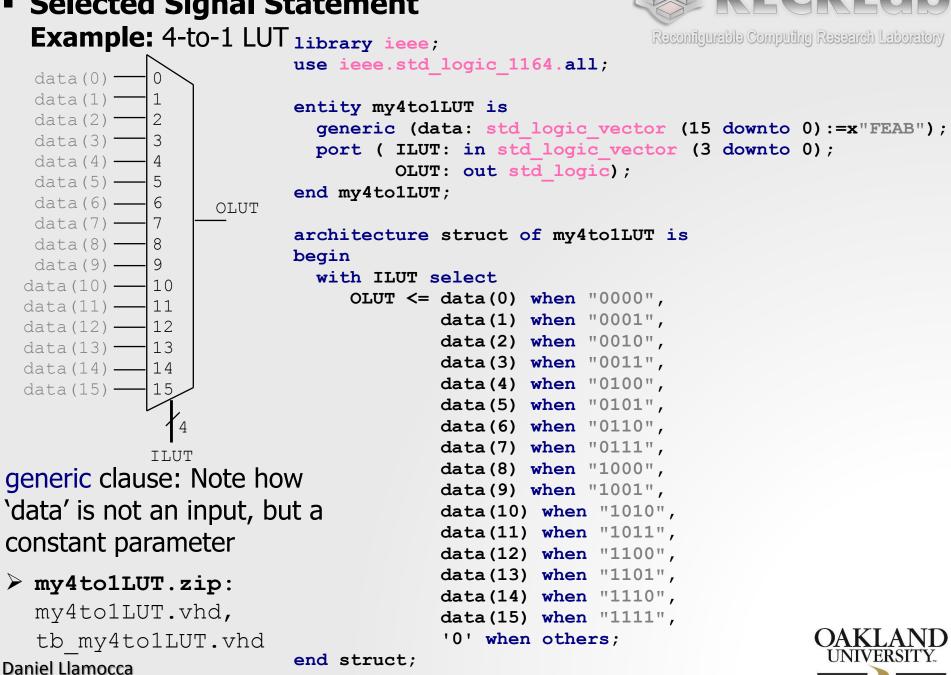

### Selected Signal Statement

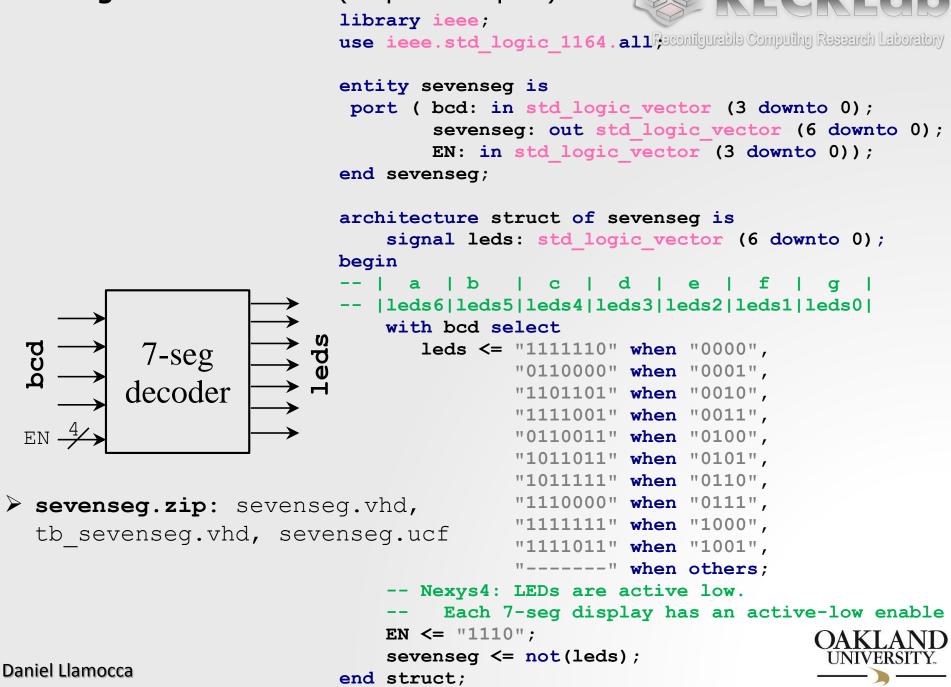

#### ■ 7-segment DECODER (outputs ≥ inputs)

Decoder 2-to-4 with enable:

```

library ieee;

use ieee.std logic 1164.all;

entity dec2to4 is

port (w: in std logic vector (1 downto 0);

E: in std logic;

y: out std logic vector (3 downto 0));

yend dec2to4;

DECODER

E

architecture struct of dec2to4 is

signal Ew: std logic vector (2 downto 0);

begin

Ew \leq E \& w; -- concatenation

with Ew select

y <= "0001" when "100",

"0010" when "101",

"0100" when "110",

"1000" when "111",

"0000" when others;

end struct;

```

- CONCURRENT ASSIGNMENT STATEMENTS :

- Conditional signal assignment: WHEN ELSE: Similarly to the selected signal assignment, this statement allows a signal to take one out of many values based on a certain condition. The syntax however is different and it allows to describe circuits in a more compact fashion.

- Example: MUX 2-to-1

If the condition on **when** is FALSE, we assign a value to 'y' after **else**. This assignment can also be conditioned by another **when-else** clause (see next example)

```

library ieee;

use ieee.std_logic_1164.all;

entity mux21_cond is

port ( a, b, s: in std_logic;

y: out std_logic);

end mux21 cond;

```

```

architecture est of mux21_cond is

begin

```

```

y <= a when s = '0' else b;

end est;

```

#### Conditional signal assignment (WHEN - ELSE):

• **Example:** MUX 4-to-1

Note that the assignment on 'b' is conditioned by another when-else clause. Same for 'c'. Only the assignemnt of 'd' is not conditioned. There is no limit to the number of nested conditions.

```

library ieee;

use ieee.std_logic_1164.all;

entity mux41_cond is

port (a, b, c, d: in std_logic;

s: in std_logic_vector (1 downto 0);

y: out std_logic);

end mux41_cond;

```

Reconfigurable Computing Research Laboratory

```

architecture est of mux41_cond is begin

```

y <= a when s = "00" else b when s = "01" else c when s = "10" else d; end est;

Conditional signal assignment (WHEN - ELSE):

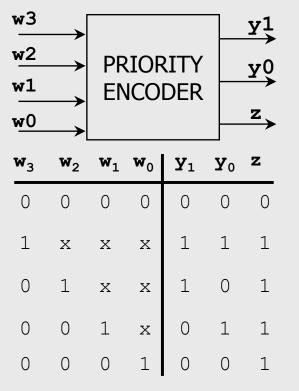

• **Example:** Priority Encoder 4-to-2

when-else has a

priority level,  $\Rightarrow$  it is easy to describe a priority encoder. With **with-select**, this circuit description would be very tedious. Daniel Llamocca

```

library ieee;

use ieee.std logic 1164.all;

entity my prienc is

port ( w: in std logic vector (3 downto 0);

y: out std logic vector (1 downto 0);

z: out std logic);

end my prienc;

architecture struct of my prienc is

begin

y \le "11" when w(3) = '1' else

"10" when w(2) = '1' else

"01" when w(1) = '1' else

"00";

z <= '0' when w = "0000" else '1';</pre>

-- If no input is '1', z is '0'

end struct;

```

Reconfigurable Computing Research Laboratory

**Example**: Priority encoder 8 to 3:

would be very tedious. > my\_prienc8to3.zip: my\_prienc8to3.vhd, tb\_my\_prienc8to3.vhd, my\_prienc8to3.ucf

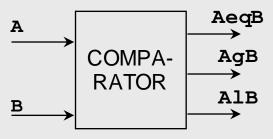

- Conditional signal assignment (WHEN ELSE);

- Example: 4-bit comparator

Reconfigurable Computing Research Laboratory

```

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all; -- unsigned #s

```

```

Note the use of the

operators `=, >, <` to

compare integer

numbers

```

```

Always indicate what

type of numbers we

are working with. In

the example we are

using unsigned

numbers. For 2's

complement, use

'signed'.

```

```

entity my_comp is

port ( A,B: in std_logic_vector (3 downto 0);

AeqB, AgB, AlB: out std_logic);

end my_comp;

```

```

architecture struct of my_comp is

begin

```

```

AeqB <= '1' when A = B else '0';

AgB <= '1' when A > B else '0';

AlB <= '1' when A < B else '0';</pre>

```

```

end struct;

```

- Conditional Signal Assignment (WHEN ELSE):

- **Example:** Demultiplexor

```

library ieee;

use ieee.std logic 1164.all;

use ieee.std logic unsigned.all;

entity my demux is

port ( s: in std logic vector (1 downto 0);

\begin{array}{c} 0 \\ 1 \\ 2 \\ 3 \\ 2 \\ 3 \\ 2 \\ s \end{array}

x: in std logic;

a,b,c,d: out std logic);

end my demux;

architecture struct of my demux is

begin

a \le x when s = "00" else '0';

b \le x when s = "01" else '0';

c \le x \text{ when } s = "10" \text{ else } '0';

```

$d \leq x$  when s = "11" else '0';

Description: Note that the order of the statements is not relevant.

end struct;

Daniel Llamocca

Concurrent

Reconfigurable Computing Research Laboratory

#### Example: 4-to-1 Bus Mux using with-select and

when-else. library ieee; use ieee.std logic 1164.all;

Reconfigurable Computing Research Laboratory

```

\begin{array}{c|c} \mathbf{a} & \mathbf{N} & \mathbf{0} \\ \mathbf{b} & \mathbf{N} & \mathbf{1} \\ \mathbf{c} & \mathbf{N} & \mathbf{2} \\ \mathbf{d} & \mathbf{N} & \mathbf{3} \\ \end{array}

```

'generic' clause: It allows the definition of signals with customizable widths.

```

entity my_busmux4to1 is

generic (N: INTEGER:= 8);

port (a,b,c,d: in std_logic_vector (N-1 downto 0);

s: in std_logic_vector (1 downto 0);

y_r, y_t: out std_logic_vector (N-1 downto 0));

end my_busmux4to1;

architecture structure of my_busmux4to1 is

begin

with s select

y_r <= a when "00",

b when "01",

c when "10",

```

```

d when others;

```

```

y_t <= a when s = "00" else

b when s = "01" else

c when s = "10" else

d;</pre>

```

end structure;

> my\_busmux4to1.zip: my\_busmux4to1.vhd, tb\_my\_busmux4to1.vh

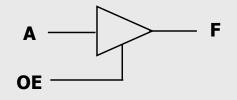

- Conditional Signal Assignment (WHEN ELSE):

- **Example:** Tri-State Buffer

```

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

```

```

entity my_tristate is

port ( A, OE: in std_logic;

F: out std_logic);

end my_tristate;

```

architecture struct of my\_tristate is

begin

$F \leq A$  when OE = '1' else 'Z';

end struct;

> my\_tristate.zip: my\_tristate.vhd, tb\_my\_stristate.vhd, my\_tristate.ucf Daniel Llamocca

Reconfigurable Computing Research Laboratory

- Conditional Signal Assignment (WHEN ELSE):

- Example: Bidirectional Port

```

DATA

WDAT

library ieee;

use ieee.std logic 1164.all; RDAT -

OE

entity my bidport is

port ( WDAT: in std logic vector(3 downto 0);

RDAT: out std logic vector(3 downto 0);

OE: in std logic;

DATA: inout std logic vector(3 downto 0));

end my bidport;

architecture struct of my bidport is

begin

DATA <= WDAT when OE = '0' else (others => 'Z');

RDAT <= DATA when OE = '1' else (others => 'Z');

end struct;

```

Reconfigurable Computing Research Laboratory

• **Example:** Bidirectional Port (test bench) Reconfigurable Computing Research Laboratory library ieee; use ieee.std logic 1164.all; To avoid data contention, entity my bidport is make sure that **DATA** =  $\mathbf{Z}$ end my bidport; when **DATA** is to be an output. architecture struct of my bidport is . . . begin uut: my bidport port map (WDAT, RDAT, OE, DATA); process begin DATA <= "ZZZZ"; wait for 100 ns; OE <= '0'; WDAT <= x''A''; DATA <= "ZZZZ"; wait for 20 ns; OE <= '1'; DATA <= x"E"; wait for 20 ns; OE <= '0'; WDAT <= x"9"; DATA <= "ZZZZ"; wait for 20 ns; OE <= '1'; DATA <= x"3"; wait for 20 ns; DATA <= x"C"; wait; end process end; OE 1110 0000 0011 DATA -1010 1001 1100 0000 1010 1001 WDAT 1110 0011 1100 RDAT > my bidport.zip: my bidport.vhd, tb my bidport.vhd Daniel Llamocca

#### ✓ INTEGER DATA TYPE

- A signal of type '*integer*' represents a binary number. But we do not specify the number of bits for the signal, only the range of decimal values (this can be very convenient).

- **Example**: 7-segment decoder. The BCD input is an integer from 0 to 9, requiring 4 bits (computed by the synthesizer).

begin

Drawback: the datatype 'integer' does not allow access to the individual bits (unlike `std\_logic\_vector')

```

use ieee.std_logic_1164.all; Reconfigurable Computing Research Laboratory

library ieee;

entity sevenseg is

port ( bcd: in integer range 0 to 9;

-- bcd: 0000 to 1001 -> 4 bits required

sevenseg: out std logic vector (6 downto 0);

EN: in std logic vector (3 downto 0));

end sevenseq;

architecture struct of sevenseg is

signal leds: std logic vector (6 downto 0);

a | b

C |

d

е

f

-- |leds6|leds5|leds4|leds3|leds2|leds1|leds0|

with bcd select

leds <= "1111110" when 0,</pre>

"0110000" when 1,

"1101101" when 2,

"1111001" when 3,

"0110011" when 4,

"1011011" when 5,

"1011111" when 6,

"1110000" when 7,

```

```

"11111111" when 8,

"1111011" when 9;

-- Nexys3: LEDs are active low.

Each 7-seg display has an active-low enable

EN <= "0111";

sevenseg <= not(leds);</pre>

end struct;

```

# • ARITHMETIC STATEMENTS:

- We can use the operators +, -, and \* for rapid Reconfigurable Computing Research Laboratory specification of arithmetic operations for integer numbers. We can also use the comparison statements: >, <, =, /=, >=, <=.</p>

- +/-: The operands and the result must have the same bit width.

- Example: Adder/subtractor implemented by multiplexing the adder and subtractor outputs:

- You <u>must</u> specify the representation for a,b (signed/unsigned):

- <u>unsigned</u> library: a-b: unsigned subtraction.

- `\_signed' library: a-b: signed (2C) subtraction

- Overflow not accounted for. Here, you might need to zero/sign-extend the input operands.

- This implements a fully combinational circuit.

Daniel Llamocca

```

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity ex_addsub is

port (a,b: in std_logic_vector (3 downto 0);

s: in std_logic;

f: out std_logic_vector (3 downto 0));

end ex_addsub;

```

```

architecture structure of ex_addsub is begin

```

```

with s select

f <= a+b when '0',

a-b when others;</pre>

```

end structure;

ex\_addsub.zip: ex\_addsub.vhd, tb\_ex\_addsub.vhd, ex\_addsub.xdc

### ARITHMETIC STATEMENTS:

Example: Multiplier (fully combinational):

- You can use the operator `\*'. Make sure the output size is correct.

- ✓ Input Operators: a (NA bits), b (NB) bits.

- ✓ Output result: f (NA+NB bits)

- Operations:

```

✓ use ieee.std_logic_unsigned.all; \rightarrow A*B treats A, B as unsigned

```

✓ use ieee.std\_logic\_signed.all;  $\rightarrow$  A\*B treats A, B as signed.

```

Important:

```

- You must select the representation (unsigned/signed) for the operands.

- `\_signed': multiplication in 2C arithmetic.

```

<u>unsigned</u>:

unsigned multiplication

```

library ieee;

```

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

```

```

-- use ieee.std_logic_signed.all;

```

```

entity mult4x4 is

```

```

port (a,b: in std_logic_vector (3 downto 0);

f: out std_logic_vector (7 downto 0));

end mult4x4;

```

# ARITHMETIC STATEMENTS

- RECRLab

- Arithmetic operators and comparison statements: Reconfigurable Computing Research Laboratory You <u>must</u> indicate the representation: signed or unsigned.

- **First Approach**: we can specify the representation for <u>all operations</u> in the .vhd file using non-standard libraries (supported by Xilinx®):

- ✓ use ieee.std\_logic\_unsigned.all; → all operations will treat data as unsigned. Here A<B, A-B treats A, B as unsigned.</li>

- ✓ use ieee.std\_logic\_signed.all; → all operations will treat data as signed. Here A<B, A-B treats A, B as signed. signal A, B, S: std\_logic\_vector (3 downto 0); f <= `1' when A < B else `0'; S <= A - B;</pre>

- **Second Approach**: using the following non-standard library, we can specify a representation for specific statements within the .vhd file:

v use ieee.std\_logic\_arith.all;

f <= `1' when unsigned(A) < unsigned(B) else `0';</pre>

S <= unsigned(A) - unsigned(B);  $\rightarrow$  unsigned subtraction!

• We can also use `signed':

S <= signed(A) -signed(B);  $\rightarrow$  signed subtraction Daniel Llamocca

#### ARITHMETIC STATEMENTS

- The library ieee.std\_logic\_arith.all Reconfigurable Computing Research Laboratory lets us perform conversions from bit vector to binary and viceversa:

- signal A: std\_logic\_vector (3 downto 0);

- signal F: integer range 0 to 15;

- conv\_integer(A): It converts the bit vector A into an integer.

- F <= conv\_integer(A); It converts A into an integer. We need to indicate the representation of A, i.e., we also must use either the ieee.std\_logic\_unsigned (or signed) library.

- F <= conv\_integer(unsigned(A)); This omits the use of the ieee.std\_logic\_unsigned (or signed) library.

- conv\_std\_logic\_vector(F,N): It converts an integer data into a vector with N bits. The representation is given by the range of N.

- F <= 5;

- A <= conv\_std\_logic\_vector (F, 4);  $\rightarrow A=0101$ .